Abstract.

This research project investigates the development and implementation of a software-defined Phase-Locked Loop (PLL) mechanism using DAHDI (Digium Asterisk Hardware Device Interface) timing synchronization tool. The goal is to achieve a software-defined, GPS (E1 line) non-dependent implementation of a physical PLL for regions where a reliable GPS signal is not available. As an alternative for starting from scratch, we are modifying the source code of DAHDI, this functions as a basement for synchronization between DAHDI itself and external systems, particularly those using the osmo-e1d protocol.

Background of the project

Phase-Locked Loops (PLLs) are fundamental components in multiple electronic systems, ranging down from communication systems to frequency synthesis. Traditionally, PLLs have

been implemented using hardware components, requiring a physical design, being GPS (or any other form of stable signal reference) dependent and manufacturing efforts. However, the advent of powerful digital signal processors (DSPs) and field-programmable gate arrays (FPGAs) has opened up new possibilities for software-defined implementations.

Phase-Locked Loops (PLLs) are fundamental components in multiple electronic systems, ranging down from communication systems to frequency synthesis. Traditionally, PLLs have

been implemented using hardware components, requiring a physical design, being GPS (or any other form of stable signal reference) dependent and manufacturing efforts. However, the advent of powerful digital signal processors (DSPs) and field-programmable gate arrays (FPGAs) has opened up new possibilities for software-defined implementations.

Motivation

By implementing this programmable PLL, the research aims to generate an efficient solution using DAHDI timing tools for situations where a reliable precision is critical and there is no warranty of availability of a GPS E1 node, leading to enhanced performance and reliability in telecommunications applications. In addition to designing and implementing drivers and logic for the PLL itself; this includes diverse approaches to PLL settings, filtering techniques,machine & deep learning approaches and synchronization methods.

Our focus for this project is not only to make a software-defined implementation of this technology (which already exixts) but to make it reference-signal independent with a precission of 10^12.

Status of the project:

Active: as 12/12/2024

Theoretical framework

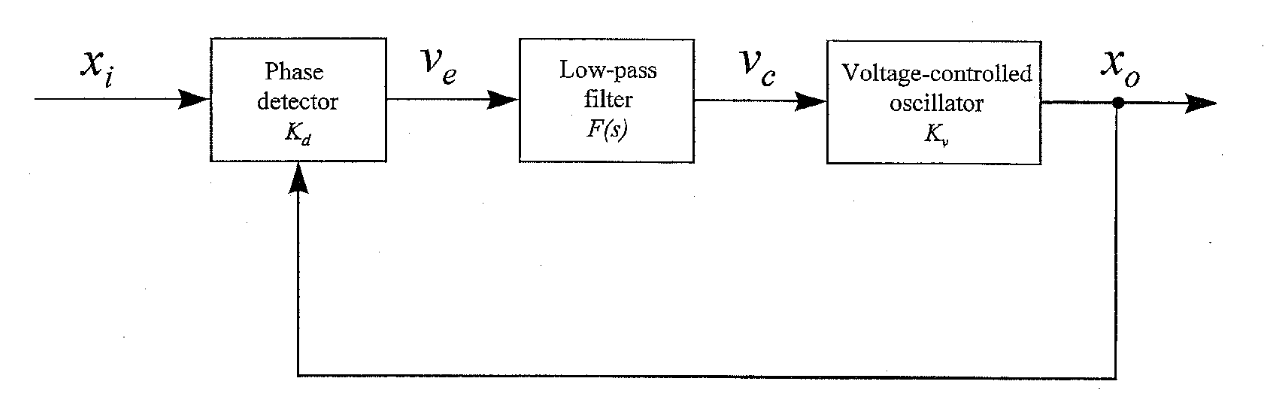

A traditional PLL operates by comparing a reference signal to a generated signal, adjustingthe frequency of the generated signal until the phase difference between the two is minimized. This process involves a phase detector, a loop filter, and a voltage-controlled oscillator (VCO). In a software-defined PLL, these components are implemented digitally using algorithms and digital hardware.

Methodology

One major challenge in software-defined PLLs is quantization noise, which arises from the finite precision of digital representations. To mitigate this issue, techniques such as delta-sigma modulation and noise shaping can be employed. Additionally, careful attention must be paid to the numerical precision of the algorithms used in the PLL, as errors in calculations can propagate and degrade the overall performance.

Basic PLL Topology:

Source: [1]

Addressing the problem

Approach:

To achieve the desired precision of 10^-12, advanced digital signal processing techniques are essential. It is important to remark that since this is still a work-in-progress project, current results do not reflect the intended functionality as this project will keep advancing.

The process began with configuring a Linux machine and compiling DAHDI from the Osmocom source code repository, utilizing its internal software timer. User space DAHDI tools and ntpd were then installed and configured to support the environment. The accuracy of the core timer was assessed using dahdi_test tool, followed by a detailed analysis of the DAHDI source code, including dahdi_test and coretimer_func, to understand their operation to be able to modify its functionality to finally implement our version's functionalities. To enable programmable time adjustments, a new field called fudge was added to the core timer structure: this is escential since our goal of making it self-regulable includes in-loop retroactive design, the implementation needs to have a way of accessing, modifying and adjusting -as necessary- the timing measurements as the next iteration is started. The coretimer_func was modified to incorporate this functionality allowing controlled variations in timing between timer calls. Additionally, new ioctl commands were introduced to enable setting and retrieving the fudge value from user space applications.

Results

The implementation of the custom fudge functionality within DAHDI successfully enabled programmable timing adjustments in the core timer. Through the addition of new ioctl commands, user space applications were able to set and retrieve the fudge value, providing a flexible interface for controlling timing parameters. Preliminary tests demonstrated that the modified DAHDI responded predictably to various fudge values, effectively altering the timing intervals between calls and validating the functionality of the introduced modifications. The integration of these adjustments into the DAHDI framework marks a significant step toward achieving precise timing synchronization.

Documents

- Software-defined PLL implementation: A Literature Review

- 32nd Joint UTEP/NMSU Workshop on Mathematics, Computer Science, and Computational Sciences Project poster

- Project Abstract

Observations

Conclusions:

The project has successfully implemented programmable timing adjustments in the DAHDI core timer through the addition of the fudge parameter, providing a flexible mechanism for fine-tuning timing intervals. This implementation is supported by newly introduced ioctl commands, enabling seamless interaction with the fudge parameter from user space applications. Further testing of the modified DAHDI framework confirmed that the fudge functionality performs as intended, offering controlled timing modifications. The ability to dynamically adjust timing intervals represents a key advancement toward achieving the intended software-defined synchronization. By validating the integration of these features, the project establishes a configurable and extensible platform for precise timing control. The modifications to the DAHDI framework not only demonstrate the feasibility of programmable timing adjustments but also provide a foundation for further enhancements, such as dynamic control algorithms and synchronization techniques.

Furure Work & directions:

Validation of Timing Performance: Test the updated DAHDI with various fudge values to assess their impact on timing performance.

Dynamic Synchronization: Modify the osmo-e1d software to monitor its FIFO length and dynamically adjust the fudge value in DAHDI, ensuring continuous synchronization.

Time-Regularization Techniques: Implement methods to regulate timing precision and stability, ensuring consistent performance under varying conditions.

AI-Assisted Adaptive Controller: Develop an AI-based adaptive controller to analyze sample patterns and dynamically optimize the initial fudge value during the first iteration, ensuring optimal initialization of the SDPLL under varying conditions.

Definition Lists

Key Concepts:

- Core Timer:

- A fundamental timing function within the DAHDI framework responsible for generating periodic interrupts to synchronize tasks..

- Fudge parameter:

- A programmable field added to the DAHDI core timer, allowing for precise time adjustments between timer calls.

- IOCTL commands:

- Input/output control system calls used in Linux to communicate between user space applications and kernel space components, enabling access to the fudge parameter in this project.

- Osmo-e1d:

- A software component used to manage communication links in telephony systems, modified in this project to dynamically adjust the fudge parameter based on system performance.